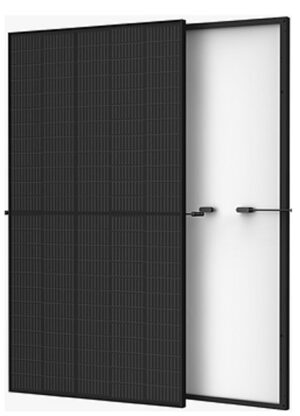

- 10BB half-cut cell technology

New circuit design, lower internal current, lower Rs loss

Ga dopped wafer, attenuation<2% (1st year) / ≤0.55% (Linear) - Significantly lower the risk of hot spot

Special circuit design with much lower hot spot temperature - Lower LCOE

2% more power generation, lower LCOE - Excellent Anti-PID performance

2 times of industry standard Anti-PID test by TUV SUD - IP68 junction box

High waterproof level